1.

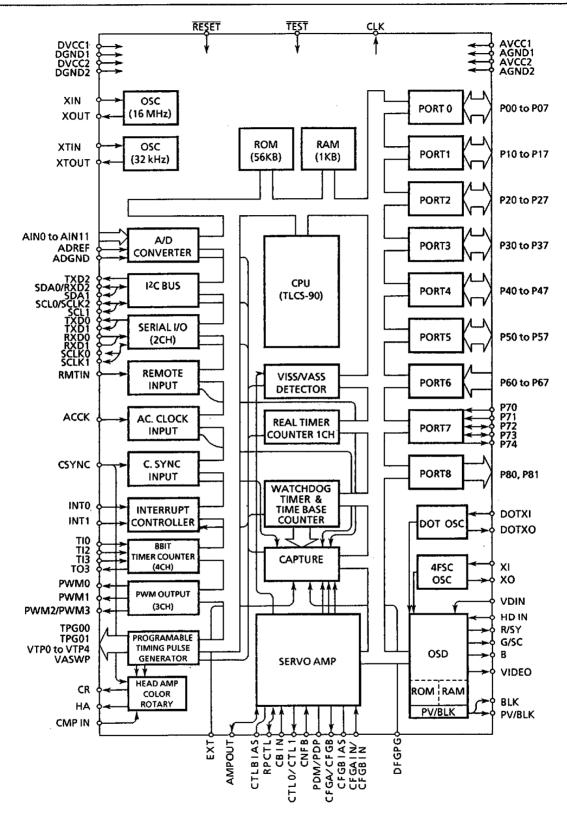

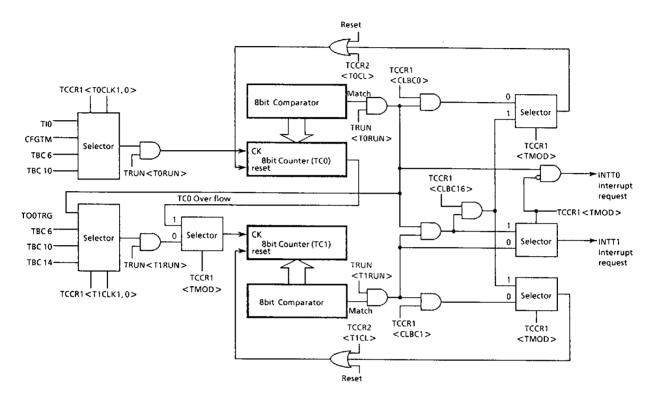

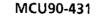

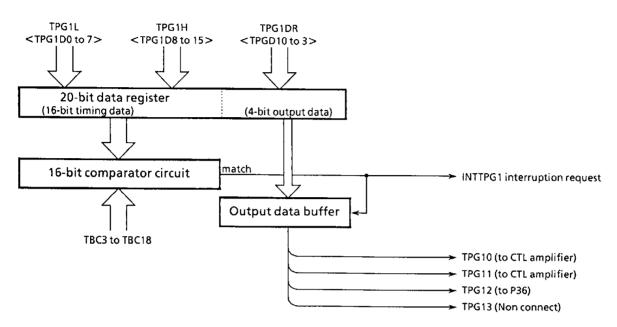

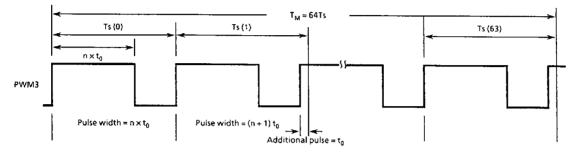

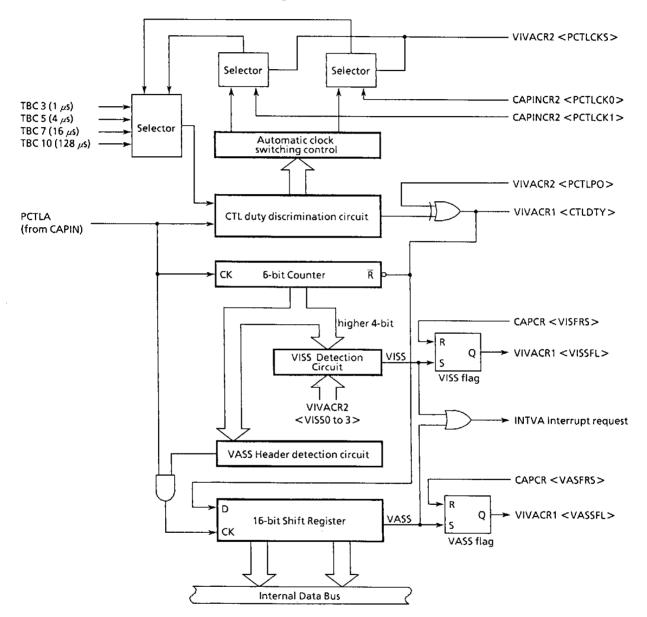

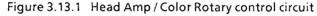

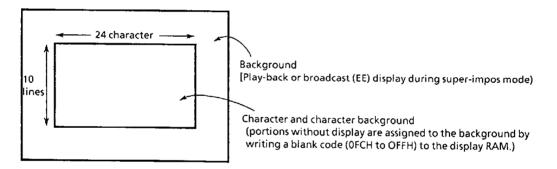

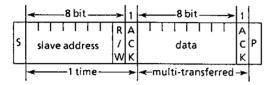

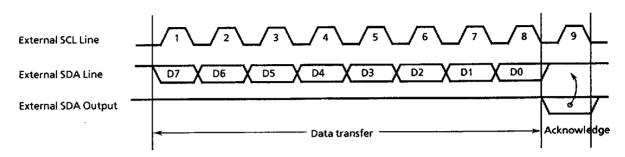

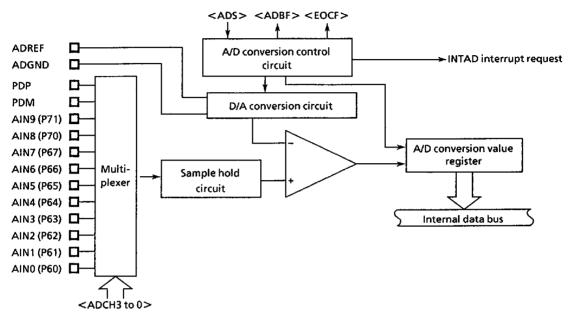

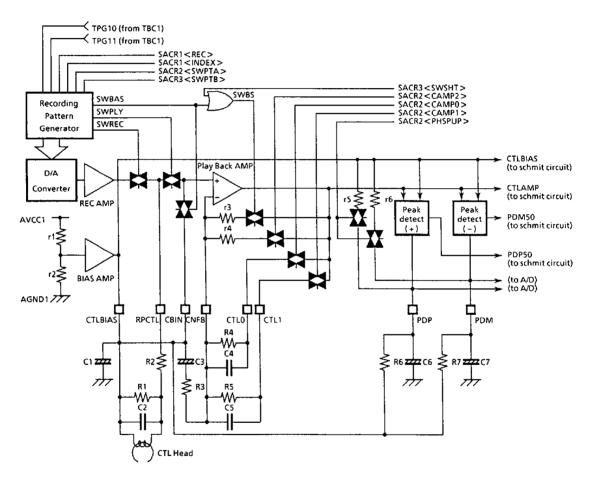

CMOS 8-BIT MICROCONTROLLER TMP90CR74ADF **OUTLINE AND CHARACTERISTICS** The TMP90CR74A is a high-performance 8-bit single-chip microcontroller; TLCS-90 CPU core capacious ROM, RAM and peripheral circuits adequate to control VCR system are included. (1) Efficiently systematized instructions 163 instructions Multiplication, division, 16-bit arithmetic operation, Bit manipulation (2) Minimum instruction execution time : 250 ns (at 16MHz Oscillation), 122  $\mu$ s (at 32.8 kHz Oscillation.) (3) Internal ROM : 56K bytes (4) Internal RAM : 1K bytes (5) 20-bit time-base Counter (TBC) (6) 8-bit timer / counter : 4 channels Timer mode / Event counter mode 16-bit timer/counter mode (7) Capture inputs : 8 terminals 18-bit timing data + 6-bit trigger data (with 8 level FIFO) 1 channel 16-bit timing data + 1-bit trigger data 2 channels (8) Timing Pulse Generator (TPG) : 2 channels 1 channel 16-bit timing data + 6-bit output data (with 4 level FIFO) 1 channel 16-bit timing data + 4-bit output data (9) PWM output 12-bit PWM : 2 channels 8-bit or 14-bit PWM : 1 channel (10) C-Sync signal separation H/V SYNC separation **Mute Detection** (11) VISS/VASS detection Index Search/Address code Search (12) Head amp/Color rotary control circuit (13) Pseudo synchronizing signal (PV/PH) output (14) Serial interface 8-bit clock synchronous mode : 2 channels I2C-BUS mode : 1 channel (15) On-Screen Display (OSD) Control circuit 256 characters 24 characters x 10 lines (16) 8-bit A/D Converter : 12 inputs (17) CTL amplifier, Capstan FG amplifier (18) Input / Output port : 63 terminals (19) Interrupt : 18 factors (20 interrupt sources) (20) Watch dog timer (21) Operation mode under low Current Consumption (Dual Clock System) STOP mode : Oscillation stop (Battery / Capacitor back-up). Port output selection (Data hold / High impedance) J.com SLOW mode : Slow speed operation with 32.8 kHz IDLE mode : CPU stop / peripheral circuit active at high speed / released by interrupt SLEEP mode : CPU stop / peripheral circuit active at slow speed / released by interrupt (22) The TMP90CR74ADF is molded in a 100-pin Quad Flat Package (QFP100-P-2222A) Purchase of TOSHIBA I<sup>2</sup> C components conveys a license under the Philips I<sup>2</sup> C Patent Rights to use these 123 components in an I<sup>2</sup> C system, provided that the system conforms to the I<sup>2</sup> C Standard Specification as defined by BUS Philips.

MCU90-389

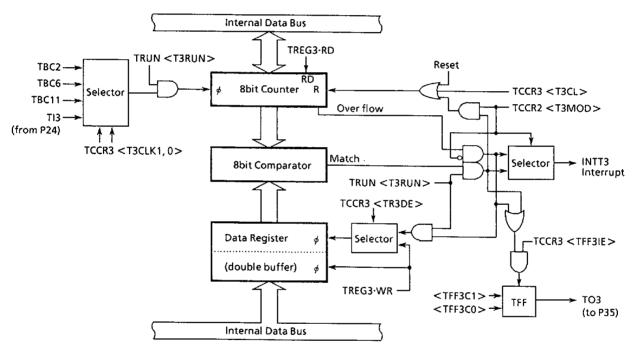

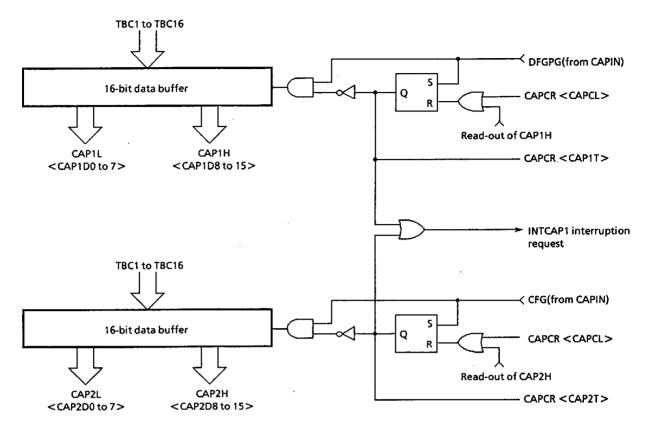

9097249 0043656 277

TMP90CR74A

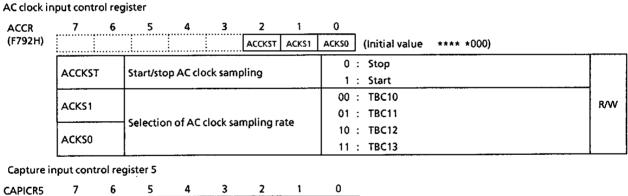

Fig 1.1 TMP90CR74ADF Block Diagram

MCU90-390

| 9097249 0043657 103 **|||**|

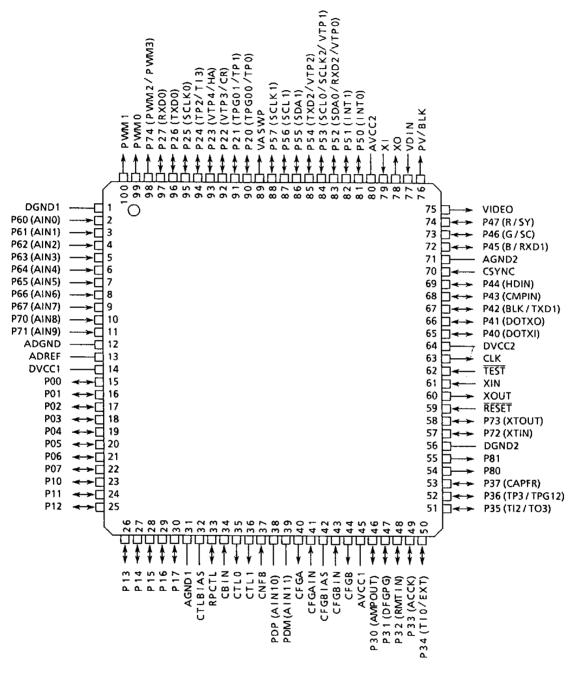

# 2. PIN ASSIGNMENT AND FUNCTIONS

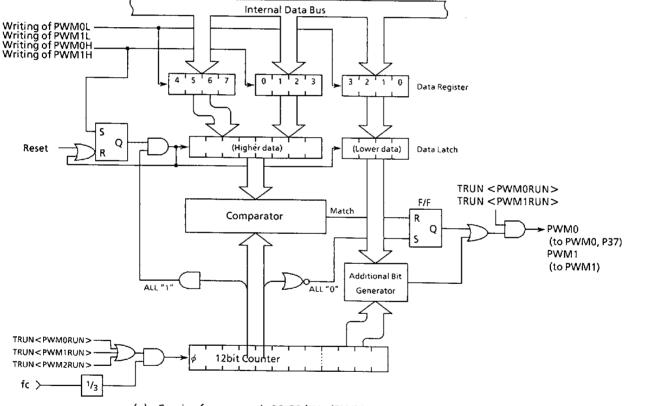

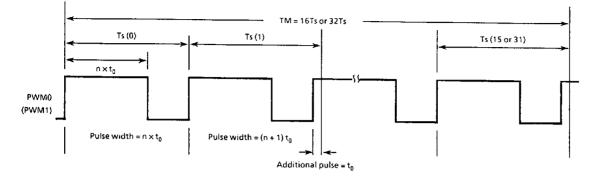

The pin assignment of TMP90CR74ADF is shown in Fig. 2.1 and its name and function are in Table 2.1.

### 2.1 Pin Assignment

9097249 0043658 047 📟

MCU90-391

2.25 **\*\*\***\*\*

# 2.2 Pin name and pin functions

The name and functions of each pin are shown in Table 2.1.

| Pin Name                                     | No. of PinS | I/O<br>Port structure        | Function                                |             |                                                                                                                                                                         |  |  |  |  |  |

|----------------------------------------------|-------------|------------------------------|-----------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

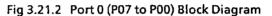

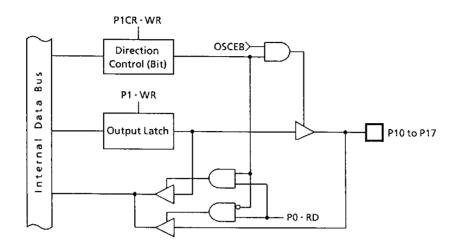

| P00 to P07                                   | 8           | I/O F<br>3-state             | P00 to P07                              | :           | 8-bit I/O port. Input and output can be set in bit unit.                                                                                                                |  |  |  |  |  |

| P10 to P17                                   | 8           | I/O F<br>3-state             | P10 to P17                              | :           | 8-bit I/O port. Input and output can be set in bit unit.                                                                                                                |  |  |  |  |  |

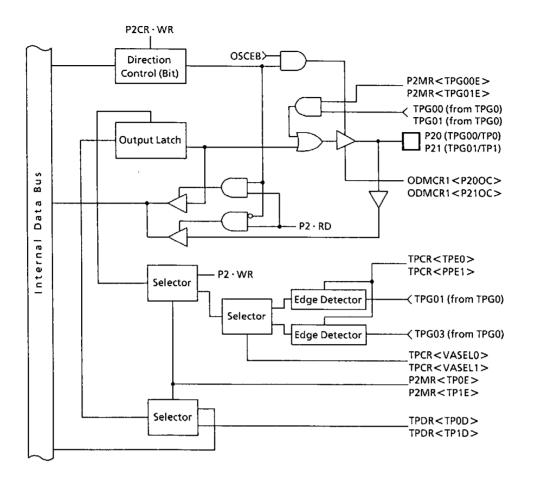

| P20<br>(TPG00 / TP0)<br>P21<br>(TPG01 / TP1) | 2           | 3-state 1                    | P20, P21<br>TPG00/TPG01<br>TP0/TP1      | ::          | 2-bit I/O port. Input and output can be set in bit unit.<br>Timing Pulse Generator 0 (TPG0)<br>Timing Pulse (TP) output.                                                |  |  |  |  |  |

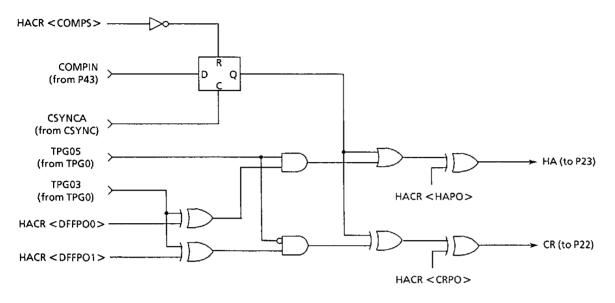

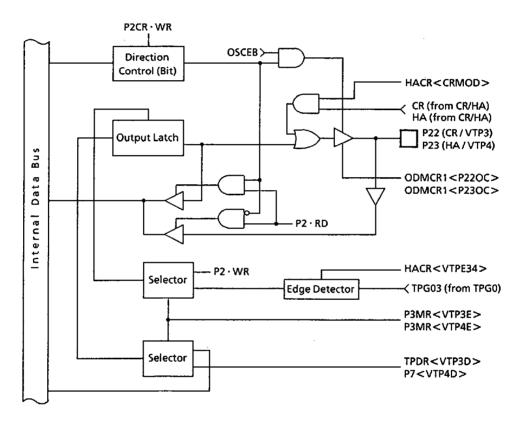

| P22<br>(VTP3/CR)<br>P23<br>(VTP4/HA)         | 2           | 3-state N<br>Programmable (  | P22, P23<br>VTP3/VTP4<br>CR<br>HA       | :<br>:<br>: | 2-bit I/O port. Input and output can be set in bit unit.<br>Video Timing pulse (VTP) output.<br>Color Rotary output.<br>Head Amp switching signal output.               |  |  |  |  |  |

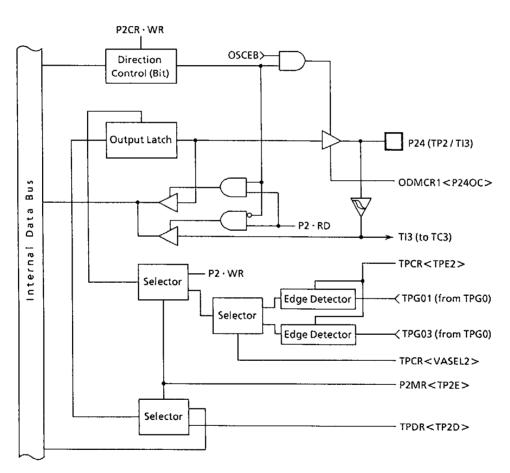

| P24 (TP2 / TI3)                              | 1           | 3-state 1                    | Р24<br>ГР2<br>ГI3                       | ::          | 1-bit I/O port. Input and output can be set in bit unit.<br>Timing pulse (TP) output.<br>Event count input for Timer3 (TC3).                                            |  |  |  |  |  |

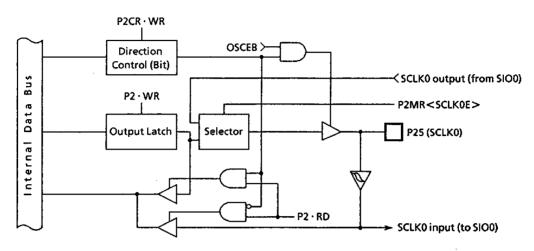

| P25 (SCLK0)                                  | 1           |                              | P25<br>SCLK0                            | :           | 1-bit I/O port. Input and output can be set in bit unit.<br>Serial clock input/output for SIO0.                                                                         |  |  |  |  |  |

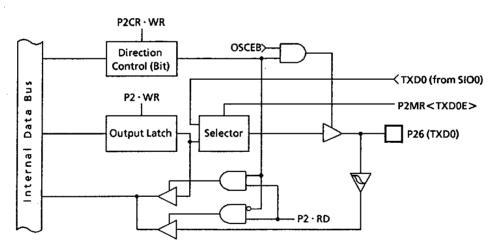

| P26 (TXD0)                                   | 1           |                              | P26<br>FXD0                             | :           | 1-bit I/O port. Input and output can be set in bit unit.<br>Serial transmit data output for SIO0.                                                                       |  |  |  |  |  |

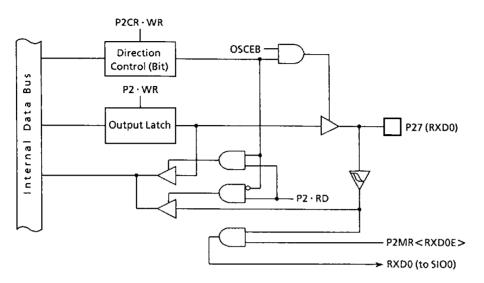

| P27 (RXD0)                                   | 1           |                              | P27<br>RXD0                             | :           | 1-bit I/O port. Input and output can be set in bit unit.<br>Serial receive data input for SIO0.                                                                         |  |  |  |  |  |

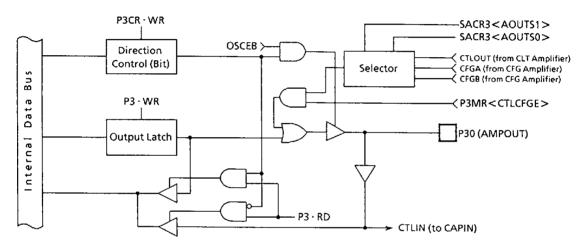

| P30<br>(AMPOUT)                              | 1           |                              | P30<br>AMPOUT                           | :           | 1-bit I/O port. Input and output can be set in bit unit.<br>Monitor output of Analog amp (CTL amp / CFG amp) for<br>servo control.                                      |  |  |  |  |  |

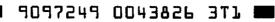

| P31 (DFGPG)<br>P32 (RMTIN)<br>P33 (ACCK)     | 3           | 3-state [<br>Schmitt input ] | P31, P32, P33<br>DFGPG<br>RMTIN<br>ACCK | ::          | 3-bit I/O port. Input and output can be set in bit unit.<br>Input for Drum PG/FG conposite signal.<br>Input for remote control signal.<br>Input for AC power frequency. |  |  |  |  |  |

| P34<br>(TIO / EXT)                           | 1           | 3-state 1                    | P34<br>F10<br>EXT                       | ::          | I/O port. Input and output can be set in bit unit.<br>Event Count input for Timer0 (TC0).<br>External trigger input for Capture 0 (CAP0).                               |  |  |  |  |  |

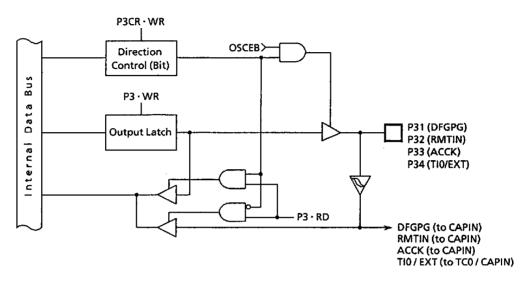

| P35<br>(T12 / TO3)                           | 1           | 3-state                      | P35<br>TI2<br>TO3                       | ::          | 1-bit I/O port. Input and output can be set in bit unit.<br>Event Count input for Timer2 (TC2).<br>Timer3 (TC3) output.                                                 |  |  |  |  |  |

Table 2.1 Pin name and pin functions (1/4)

MCU90-392

🛛 9097249 0043659 T&6 🎟

| Pin Name                                              | No. of Pins | I/O<br>Port structure                                  |                                                         | Function                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------|-------------|--------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

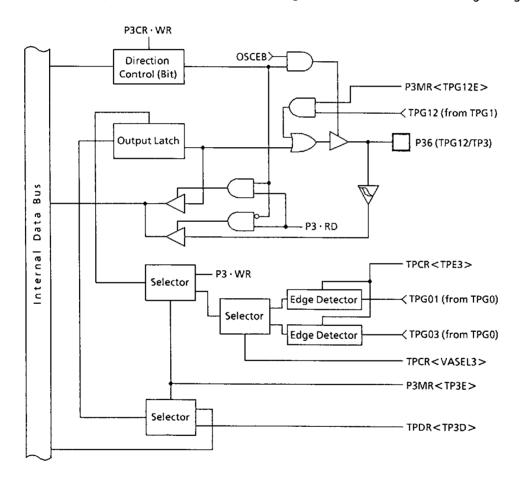

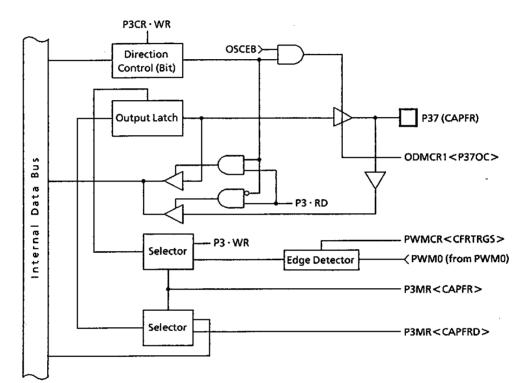

| P36<br>(TP3 / TPG12)                                  | 1           | 3-state                                                | P36<br>TP3<br>TPG12                                     | <ul> <li>1-bit I/O port. Input and output can be set in bit unit.</li> <li>Timing pulse (TP) output.</li> <li>Timing pulse generator (TPG1) output.</li> </ul>                                                                                                                                                    |

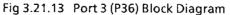

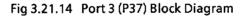

| P37 (CAPFR)                                           | 1           |                                                        | P37<br>CAPFR                                            | <ul> <li>1-bit I/O port. Input and output can be set in bit unit.</li> <li>Capstan motor control output.</li> </ul>                                                                                                                                                                                               |

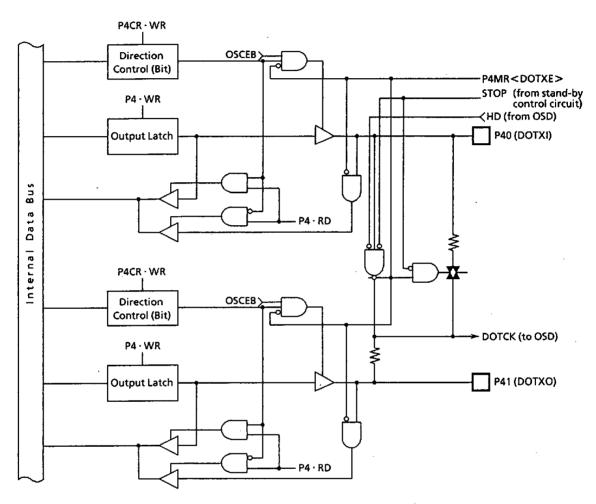

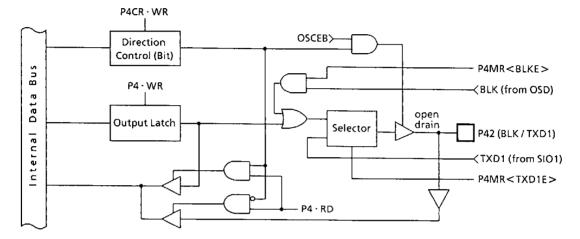

| P40 (DOTXI)<br>P41 (DOTXO)                            | 2           | ł I                                                    | P40, P41<br>DOTXI / DOTXO                               | <ul> <li>2-bit I/O port. Input and output can be set in bit unit.</li> <li>Oscillator terminal for OSD dot-clock.</li> </ul>                                                                                                                                                                                      |

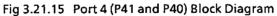

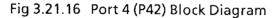

| P42<br>(BLK / TXD 1)                                  | 1           | Open Drain                                             | P42<br>BLK<br>TXD1                                      | <ul> <li>1-bit I/O port. Input and output can be set in bit unit.</li> <li>Blanking output for OSD.</li> <li>Serial transmit data output for SIO1.</li> </ul>                                                                                                                                                     |

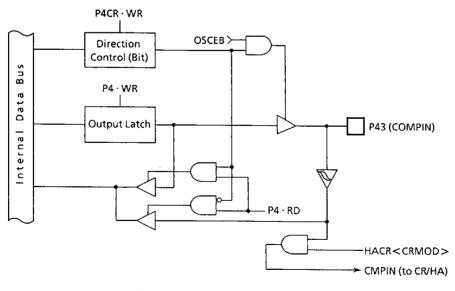

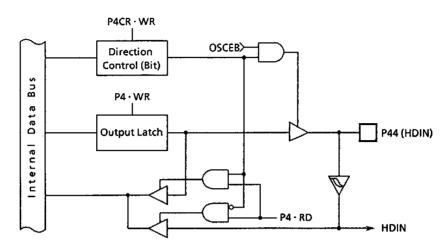

| P43 (CMPIN)<br>P44 (HDIN)                             | 2           | 3-state                                                | P43, P44<br>CMP IN<br>HD IN                             | <ul> <li>2-bit I/O port. Input and output can be set in bit unit.</li> <li>Comparator signal input for Head Amp switch.</li> <li>Horizontal sync. signal input.</li> </ul>                                                                                                                                        |

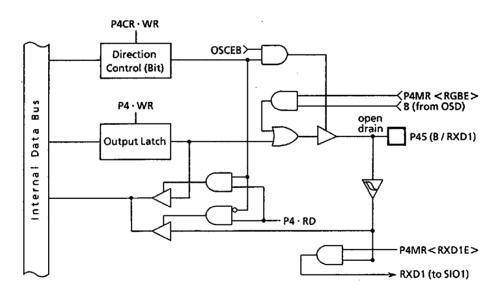

| P45<br>(B/RXD1)                                       | 1           | Open Drain                                             | P45<br>B<br>RXD1                                        | <ul> <li>1-bit I/O port. Input and output can be set in bit unit.</li> <li>Blue output from OSD.</li> <li>Serial receive data input for SIO1.</li> </ul>                                                                                                                                                          |

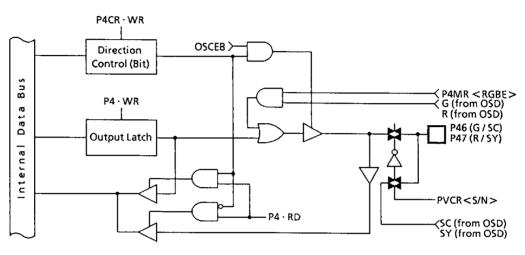

| P46 (G / SC)<br>P47 (R / SY)                          | 2           | 3-state                                                | P46, P47<br>G, R<br>SC, SY                              | <ul> <li>2-bit I/O port. Input and output can be set in bit unit.</li> <li>Green and Red output from OSD.</li> <li>Chroma, luminance Signal output from OSD.</li> </ul>                                                                                                                                           |

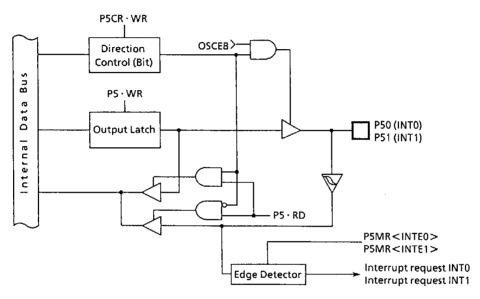

| P50 (INT0)<br>P51 (INT1)                              | 2           | 1 1                                                    | P50, P51<br>INTO, INT1                                  | <ul> <li>2-bit I/O port. Input and output can be set in bit unit.</li> <li>External interrupt request.</li> </ul>                                                                                                                                                                                                 |

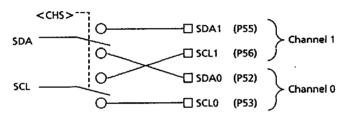

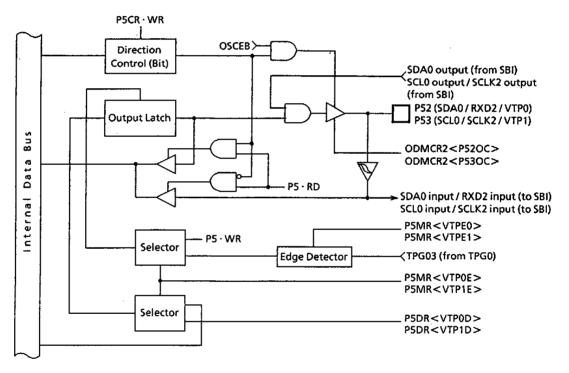

| P52 (SDA0/<br>RXD2/VTP0)<br>P53 (SCL0/<br>SCLK2/VTP1) | 2           | 3-state<br>Programmable<br>Open Drain<br>Schmitt input | P52, P53<br>SDA0<br>SCL0<br>RXD2<br>SCLK2<br>VTP0, VTP1 | <ul> <li>2-bit I/O port. Input and output can be set in bit unit.</li> <li>Serial data I/O for I<sup>2</sup>CBUS.</li> <li>Serial clock I/O for I<sup>2</sup>CBUS.</li> <li>Serial receive data input for SIO2.</li> <li>Serial clock input/output for SIO2.</li> <li>Video timing pulse (VTP) output.</li> </ul> |

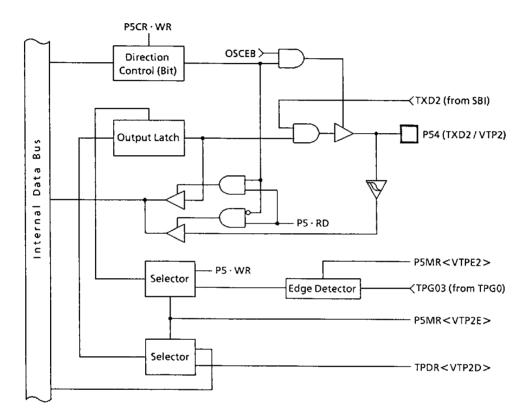

| P54 (TXD2/<br>VTP2)                                   | 1           | 3-state                                                | P54<br>TXD2<br>VTP2                                     | <ul> <li>1-bit I/O port. Input and output can be set.</li> <li>Serial transmit data output for SIO2.</li> <li>Video timing pulse (VTP) output.</li> </ul>                                                                                                                                                         |

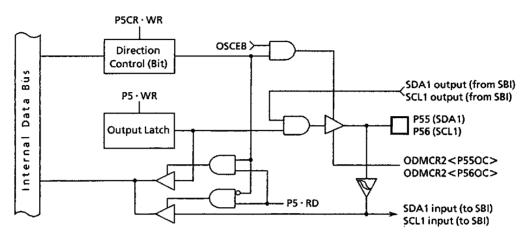

| P55 (SDA1)<br>P56 (SCL1)                              | 2           | 3-state                                                | P55, P56<br>SDA1<br>SCL1                                | <ul> <li>2-bit I/O port. Input and output can be set in bit unit.</li> <li>Serial data input/output for I<sup>2</sup>CBUS.</li> <li>Serial clock input/output for I<sup>2</sup>CBUS.</li> </ul>                                                                                                                   |

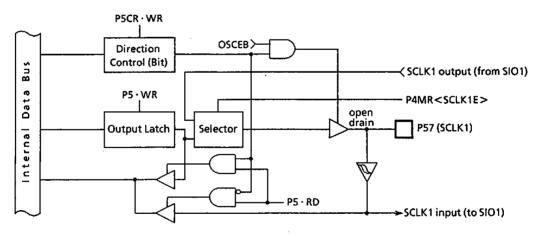

| P57 (SCLK1)                                           | 1           | 1                                                      | P57<br>SCLK1                                            | <ul> <li>1-bit I/O port. Input and output can be set.</li> <li>Serial clock input/output for SIO1.</li> </ul>                                                                                                                                                                                                     |

Table 2.1 Pin name and pin functions (2/4)

MCU90-393

🗰 9097249 0043660 7T8 🎟

.

| Pin Name                                                   | No. of Pins | I/O<br>Port structure                           | Function                                                                                                                                                           |  |  |  |  |  |  |  |

|------------------------------------------------------------|-------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

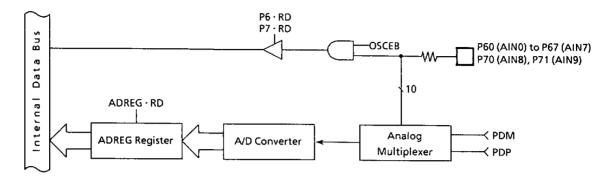

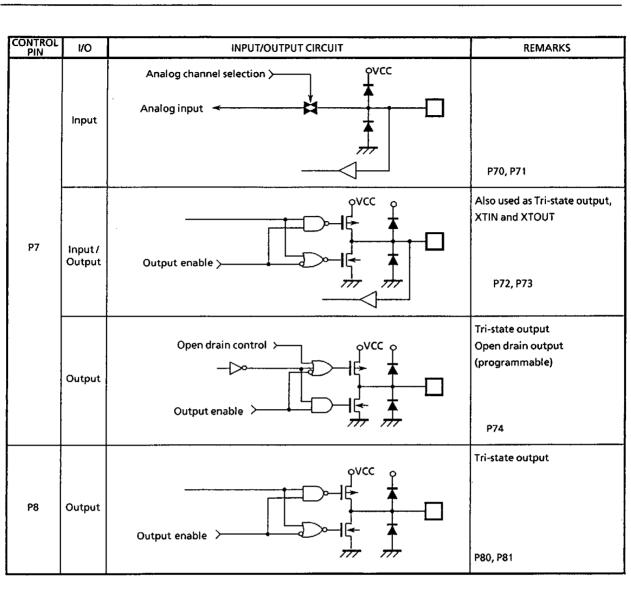

| P60 (AIN0) to<br>P67 (AIN7)<br>P70 (AIN8) to<br>P71 (AIN9) | 10          | Input                                           | P60 to P67 : 8-bit input port.<br>P70, P71 : 2-bit input port.<br>AIN0 to AIN9 : Analog input for A/D converter.                                                   |  |  |  |  |  |  |  |

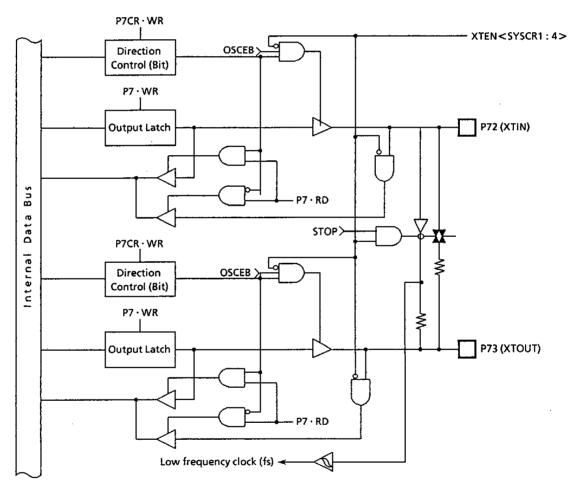

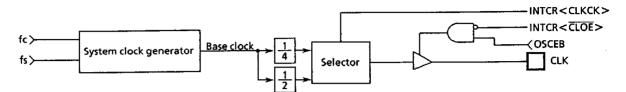

| P72 (XTIN)<br>P73 (XTOUT)                                  | 2           | I/O<br>3-state                                  | P72, P73       :       2-bit I/O port. Input and output can be set in bit unit.         XTIN, XTOUT       :       Oscillator terminals for slow clock (32.768 kHz) |  |  |  |  |  |  |  |

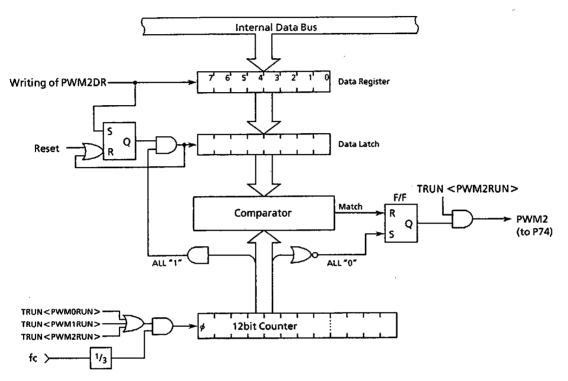

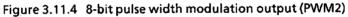

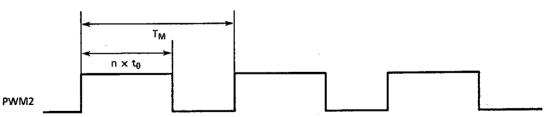

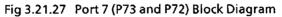

| P74 (PWM2 /<br>PWM3)                                       | 1           | Output<br>3-state<br>Programmable<br>Open Drain | P74 : 1-bit output port.<br>PWM2/PWM3 : 8-bit / 14-bit PWM (PWM2 / PWM3) output.                                                                                   |  |  |  |  |  |  |  |

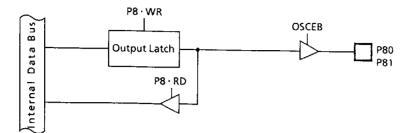

| P80<br>P81                                                 | 2           | Output<br>3-state                               | P80, P81 : 2-bit output port.                                                                                                                                      |  |  |  |  |  |  |  |

| PWM0<br>PWM1                                               | 2           | Output<br>3-state<br>Programmable<br>Open Drain | PWM0       : 12-bit PWM (PWM0) output.         PWM1       : 12-bit PWM (PWM1) output.                                                                              |  |  |  |  |  |  |  |

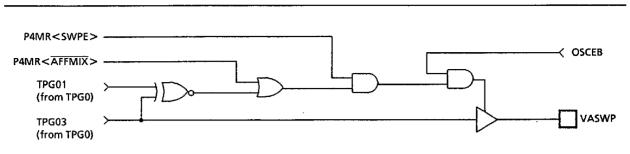

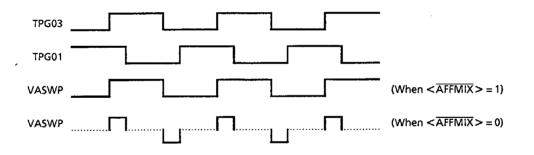

| VASWP                                                      | 1           | Output<br>3-state                               | Video / Audio head switching control signal output.                                                                                                                |  |  |  |  |  |  |  |

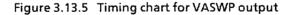

| CSYNC                                                      | 1           | Input<br>Schmitt input                          | Composite sync. signal input.                                                                                                                                      |  |  |  |  |  |  |  |

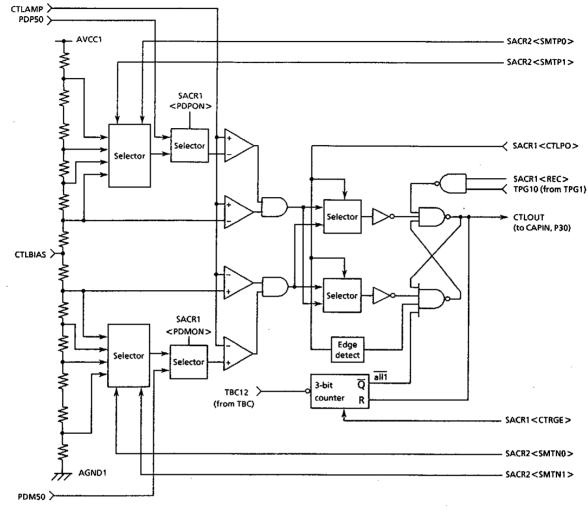

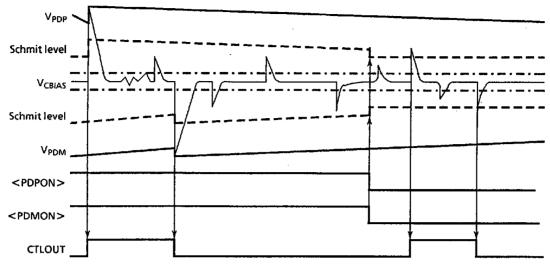

| CTLBIAS                                                    | 1           | -                                               | Bias terminal for control (CTL) amplifier.                                                                                                                         |  |  |  |  |  |  |  |

| RPCTL                                                      | 1           | I/O                                             | Input and output for Control (CTL) signal.                                                                                                                         |  |  |  |  |  |  |  |

| CBIN                                                       | 1           | Input                                           | Bias input terminal for control (CTL) amplífier.                                                                                                                   |  |  |  |  |  |  |  |

| CTL0<br>CTL1                                               | 2           | Output                                          | CTL amplifier output for gain switching.                                                                                                                           |  |  |  |  |  |  |  |

| CNFB                                                       | 1           | Input                                           | Negative feed-back terminal of CTL amplifier.                                                                                                                      |  |  |  |  |  |  |  |

| PDP (AIN10)                                                | 1           |                                                 | PDP : Terminal for Peak-Hold capacitor which keeps plus<br>(positive) peak for control (CTL) Amplifier.<br>AIN10 : Analog input for PDP level monitor.             |  |  |  |  |  |  |  |

| PDM (AIN11)                                                | 1           |                                                 | PDM : Terminal for Peak-Hold capacitor which keeps plus<br>(positive) peak for control (CTL) Amplifier.<br>AIN11 : Analog input for PDM level monitor.             |  |  |  |  |  |  |  |

Table 2.1 Pin name and pin functions (3/4)

MCU90-394

🔳 9097249 0043661 634 🔳

| Pin Name       | No. of Pins | I/O<br>Port structure  | Function                                                                                                                         |

|----------------|-------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| CFGA           | 1           | Output                 | Capstan FG amplifier (CFGA amp.) output.                                                                                         |

| CFGA IN        | 1           | Input                  | Capstan FG amplifier (CFGA amp.) input.                                                                                          |

| CFG BIAS       | 1           | _                      | Capstan FG amplifier bias terminal.                                                                                              |

| CFGB IN        | 1           | Input                  | Capstan FG amplifier (CFGB amp.) input.                                                                                          |

| CFGB           | 1           | Output                 | Capstan FG amplifier (CFGB amp.) output.                                                                                         |

| VIDEO          | 1           | Output                 | OSD video signal output.                                                                                                         |

| PV/BLK         | 1           | Output<br>4-state      | Pseudo V-SYNC (PV) output / On Screen Display (OSD) Blanking (BLK) output.                                                       |

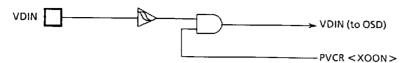

| VDIN           | 1           | Input<br>Schmitt input | Vertical sync signal input.                                                                                                      |

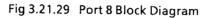

| XI, XO         | 2           | Input, Output          | Oscillator terminals for 4fsc clock of OSD                                                                                       |

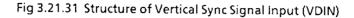

| CLK            | 1           | Outpuț                 | Clock output : 1/2 or 1/4 of system clock (16 MHz) is output. During RESET operation, output stays high. (Pulled up internally). |

| TEST           | 1           | Input                  | Test terminal : Should be connected to high.                                                                                     |

| XIN, XOUT      | 2           | Input, Output          | Oscillator terminals for main clock (16 MHz)                                                                                     |

| RESET          | 1           | Input<br>Schmitt input | System reset input.                                                                                                              |

| DVCC1<br>DVCC2 | 2           | -                      | Digital Power supply.                                                                                                            |

| DGND1<br>DGND2 | 2           | -                      | Digital Ground.                                                                                                                  |

| AVCC1<br>AVCC2 | 1           | -                      | Analog Power supply.                                                                                                             |

| AGND1<br>AGND2 | 1           | -                      | Analog Ground.                                                                                                                   |

| ADREF          | 1           | -                      | A/D converter reference voltage.                                                                                                 |

| ADGND          | 1           | -                      | A/D converter Ground.                                                                                                            |

| Table 2.1 | Pin name and pin functions (4/4) |

|-----------|----------------------------------|

|           |                                  |

MCU90-395

### 3. OPERATION

This chapter describes the functions and the basic operations of the TMP90CR74A in every block.

### 3.1 CPU

TMP90CR74A includes a high performance 8 bit CPU. For the function of the CPU, see the previous chapter "TLCS-90 CPU". This chapter explains exclusively the functions of the CPU of TMP90CR74A which are not described in the chapter "TLCS-90 CPU".

### 3.1.1 Reset

In order to reset the TMP90CR74A, the RESET input must be maintained at the "0" level for at least ten system clock cycles (10 states : 1.25 Is at 16 MHz) within an operating voltage band and with a stable oscillation. When a reset request is accepted, all I/O ports and internal registers are initialized. The registers of the CPU remain unchanged. Note, however, that the program counter PC, the interrupt enable flag IFF are cleared to "0". Register A shows an undefined status.

When the reset is cleared, the CPU starts executing instructions from the address 0000H.

### 3.1.2 EXF (Exchange Flag)

For TMP90CR74A, "EXF", which is inverted when the instuction "EXX" is executed to transfer data between the main register and the auxiliary register, is allocated to the watch dog timer control register 2 (WDTCR2<EXF> : bit 1 of memory address FFFBH).

| WDTCR2  | 7   | 6 | 5       | 4      | 3    | 2 | 1   | 0                                             |   |

|---------|-----|---|---------|--------|------|---|-----|-----------------------------------------------|---|

| (FFFBH) |     |   | TBC1F   | TBC0F  | WDTE |   | EXF | DRVE                                          |   |

|         | EXF |   | Exchang | e Flag |      |   |     | Invert each time EXX instruction is executed. | R |

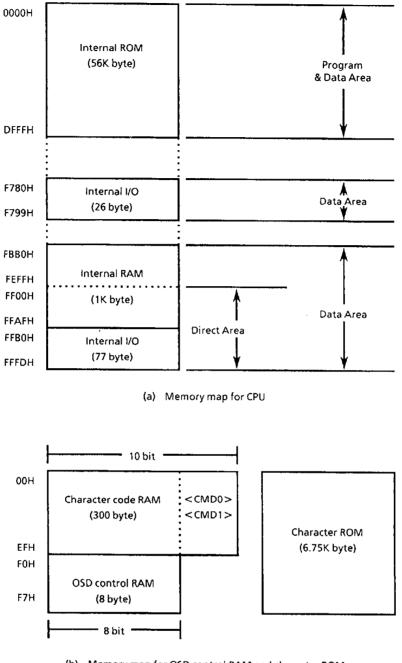

### 3.2 Memory Map

### 3.2.1 Internal ROM

The TMP90CR74A contains an 56K-byte ROM. The address space from 0000H to DFFFH is provided to the ROM. The CPU starts executing a program from 0000H by resetting.

The addresses 0008H to 004FH in this internal ROM area are used for the entry area for the interrupt processing.

#### 3.2.2 Internal RAM

The TMP90CR74A also contains a 1K-byte RAM, which is allocated to the address space from FBB0H to FFAFH. The CPU allows the access to a certain RAM area (FF00H to FFAFH, 176 bytes) by a short operation code (opcode) in a "direct addressing mode".

### 3.2.3 Internal I/O

The TMP90CR74A provides a 103-byte address space as an internal I/O area, whose addresses range from FFB0H to FFFDH (I/O area 1) and F780H to F799H (I/O area 2). This I/O area 1 can be accessed by the CPU using a short opcode in the "direct addressing mode".

Figure 3.2.1 is a memory map indicating the areas accessible by the CPU in the respective addressing mode.

(b) Memory map for OSD control RAM and character ROM

### Figure 3.2.1 Memory map

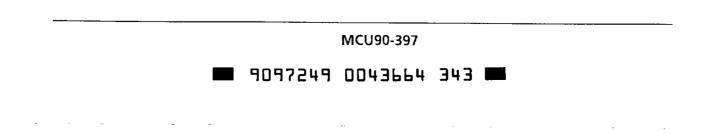

### 3.3 SYSTEM CLOCK CONTROL

The System Clock Controller consists of Clock Generator, Timing Generator, Standby Controller and Read Time Counter (RTC).

Figure 3.3.1 System Clock Controller

### 3.3.1 Clock Generator

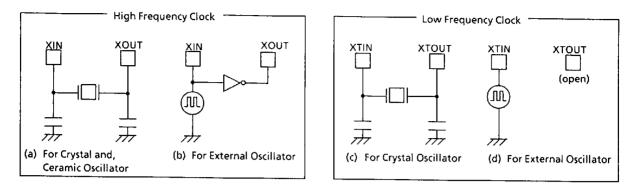

The Clock Generator is a circuit which generates a basic clock for the system clock; the system clock is provided for CPU and peripheral hardwares. This Clock Generator contains 2 types of oscillating circuit : for high frequency clock and for low frequency clock. Oscillating circuit for the system clock can be selected on Standby Controller, and the current consumption can be reduced by selecting low-speed operation.

High frequency clock (fc) and low frequency clock (fs) are obtained by connecting oscillator between terminals XIN and XOUT and between terminals XTIN and XTOUT respectively. Clock input from external oscillator is also available.

Figure 3.3.2 Connecting Oscillator

MCU90-399

🗰 9097249 0043666 lle 🖿

### 3.3.2 Timing Generator

The timing generator generates sorts of system clock from the basic clock (fc or fs), providing for CPU core and peripheral hardwares.

(1) Architecture

The timing generator consists of the system clock generator and the time base counter (TBC) which generates system clock for peripheral hardwares. After resetting, the system clock is generated from high frequency clock (fc) (NORMAL mode). Both Executing the instruction and operating the internal hardwares are synchronized by this system clock.

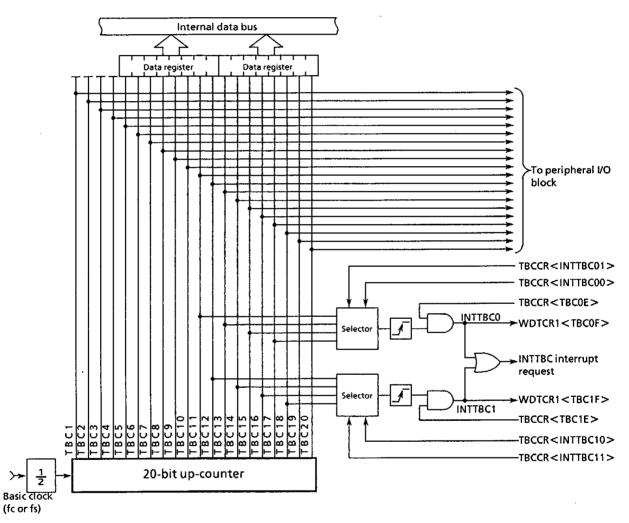

(2) Time Base Counter

The time base counter consists of a 20-bit up-counter counted by a basic clock divided-by 2 (fc/2 or fs/2), 16-bit data register and control register.

Figure 3.3.3 Shows the structure of the time-base counter (TBC).

MCU90-400

9097249 0043667 052 |

Time Base Counter Control Register

| TBCCR     | 7         | 6        | 5          | 4        | 3            | 2            | 1            | 0            |                                    |

|-----------|-----------|----------|------------|----------|--------------|--------------|--------------|--------------|------------------------------------|

| (F798H)   |           |          | TBCIE      | TBCOE    | INT<br>TBC11 | INT<br>TBC10 | INT<br>TBC01 | INT<br>TBCOO | (Reset Value **00 0000)            |

|           | TBC1E     |          |            |          |              |              |              | 00           | : INTTBC Interrupt Disable         |

|           |           |          | INTTBC I   | nterrup  | t            |              |              | 01           | : INTTBC0 Interrupt Enable         |

|           | TBCOE     |          | Enable/    | Disable  |              |              |              | 10           | : INTTBC1 Interrupt Enable         |

|           |           |          | I          |          |              |              |              | 11           | : INTTBC0/INTTBC1 Interrupt Enable |

|           | INTTBO    | 11       | INTTBC1    | Interru  | pt           |              |              |              | : TBC12<br>: TBC14                 |

|           | INTTBO    | -10      | Source C   |          |              |              |              |              | : TBC16                            |

|           |           | _ 10     |            |          |              |              |              | 11           | : TBC18                            |

|           | INTTBO    | -01      |            |          |              |              |              | 00           | : TBC11                            |

|           |           |          | INTTBCO    |          |              |              |              | 01           | : TBC13                            |

|           | INTTBO    | 200      | Source C   | lock Sel | ection       |              |              | 10           | : TBC15                            |

|           |           |          |            |          |              |              |              | 11           | : TBC17                            |

| Time Base | e Countei | r Data I | Register 1 |          |              |              |              |              |                                    |

| TBCDR1    | 7         | 6        | 5          | 4        | 3            | 2            | 1            | 0            |                                    |

| (FF82H)   | TBC12     | TBC11    | TBC10      | твс9     | TBC8         | TBC7         | TBC6         | TBC5         | (Reset Value) 0000-0000) Read only |

| Time Base | Counter   | r Data I | Register 2 | 2        |              |              |              |              |                                    |

| TBCDR2    | 7         | 6        | 5          | 4        | 3            | 2            | 1            | 0            |                                    |

| (FFB3H)   | TBC20     | TBC19    | TBC18      | TBC17    | TBC16        | T8C15        | TBC14        | TBC13        | (Reset Value 0000 0000) Read only  |

| Watchdo   | g Timer C | Iontrol  | Register   | 1        |              |              |              |              |                                    |

| WDTCR1    | 7         | 6        | 5          | 4        | 3            | 2            | 1            | 0            |                                    |

| (FFFBH)   |           |          | TBC1F      | TBCOF    | WDTE         | ]            | EXF          | DRVE         |                                    |

|           |           |          |            |          |              |              |              | 0 (W)        | : Clear                            |

|           | TBC1F     |          | INTTBC1    |          |              |              |              | 1 (W)        | : -                                |

|           | IBCIE     |          |            | interru  | prikedu      | estriag      |              | 0 (R)        | : No interrupt request             |

|           |           |          |            |          |              |              |              | 1 (R)        | : Interrupt request R/W            |

|           |           |          |            |          |              |              |              |              | : Ciear                            |

|           | TBCOF     |          | INTTBCO    | Interru  | pt Reau      | est Flag     |              | 1 (W)        |                                    |

|           |           |          |            |          |              | y            |              | 0 (R)        | : No interrupt request             |

### ① Operation

The time-base counter outputs (TBC1 to TBC20) are used as clock source or timing data for Timer/Counter, Capture (CAP0/CAP1/CAP2), timing pulse generator (TPG), and other peripheral I/O blocks. The contents of time-base counter outputs TBC5 to TBC20 can be read by reading the time-base counter data registers, TBCDR1 and TBCDR2. Note that the data registers must be read in order of TBCDR1 and then TBCDR2.

1 (R) : Interrupt request

Time-base counter interrupt requests (INTTBC) can be generated on the rising edges of counter outputs TBC11 to TBC18. The interrupt source is selected by the time-base counter control register TBCCR <INTTBC11, INTTBC10, INTTBC01, and INTTBC00>. The INTTBC interrupt requests are comprised of two interrupt request signals INTTBC0 and INTTBC1 that are logical OR' ed to generate an interrupt request. Which interrupt is requested can be identified by reading the watchdog timer control register 1 WDTCR1 <TBC0F> and <TBC1F>.

The INTTBCO flag <TBCOF> and INTTBC1 flag <TBC1F> can be cleared by writing "0" in the register.

Table 3.3.1 lists the interval time of time-base counter outputs.

|                      |       |       | •                  |       |                    |                    |                    |       |       |                    |

|----------------------|-------|-------|--------------------|-------|--------------------|--------------------|--------------------|-------|-------|--------------------|

|                      | TBC1  | TBC2  | TBC3               | TBC4  | TBC5               | TBC6               | TBC7               | TBC8  | TBC9  | TBC10              |

| Interval Time<br>[s] | 22/f  | 23/ f | 24/f               | 25/f  | 26/f               | 27/f               | 2 <sup>8</sup> /f  | 29/f  | 210/f | 211/f              |

| at 16 MHz<br>[µs]    | 0.25  | 0.5   | 1.0                | 2.0   | 4.0                | 8.0                | 16.0               | 32.0  | 64.0  | 128.0              |

|                      | TBC11 | TBC12 | TBC13              | T8C14 | T8C15              | TBC16              | TBC17              | TBC18 | TBC19 | TBC20              |

|                      | 212/f | 213/f | 2 <sup>14</sup> /f | 215/f | 2 <sup>16</sup> /f | 2 <sup>17</sup> /f | 2 <sup>18</sup> /f | 219/f | 220/f | 2 <sup>21</sup> /f |

|                      | 256.0 | 512.0 | 1024               | 2048  | 4096               | 8192               | 16384              | 32768 | 65536 | 131072             |

Table 3.3.1 interval time of Time-base Counter (f = fc)

### 3.3.3 Standby-Controling Circuit

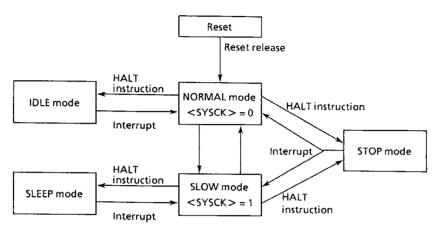

Standby-controling circuit operates for oscillator (high frequency clock, low frequency clock) oscillate/stop and system clock switching. The TMP90CR74A has five operation modes : NORMAL, IDLE, SLOW, SLEEP, and STOP. System control registers (SYSCR1 and SYSCR2) are used to switch between these operation modes. Figure 3.3.4 shows an operation mode transition diagram and the device status in each operation mode.

NORMAL mode

This mode is to operate CPU core and peripheral hardwares under high frequency clock (fc). The mode after resetting is NORMAL mode (only high frequency clock oscillates).

② IDLE mode

In this mode, the CPU is halted, with the peripheral hardware operated by the high-frequency clock (fc). (Refer to the device status in each operation mode in Figure 3.3.4 (b).) To set IDLE mode, set WDTCR2<HALTM1, HALTM0> to IDLE mode previously, and execute HALT instruction. This IDLE mode is released by interrupt, which comes from peripheral hardwares or external input; afterwards the device becomes NORMAL mode again. When IFF (interrupt enable flag of CPU) is "1" (interrupt is enabled), the device returns to normal operation after the interrupt operation. When IFF is "0" (interrupt is disabled), the device restart from the instruction following HALT for IDLE mode.

### ③ SLOW mode

In this mode, the high-frequency clock is made to stop oscillating, with the CPU core and peripheral hardware operated by the low-frequency clock (fs), thus helping to save power consumption greatly. (Refer to the device status in each operation mode in Figure 3.3.4 (b).) Before the SLOW mode is used, the Low-frequency clock (fs) must already be oscillating at the beginning of your application program after the device is cleared of a reset. Switch over from NORMAL to SLOW modes and from SLOW to NORMAL modes are controlled by the system control register <\$YSCR1 or \$YSCK2>.

#### ④ SLEEP mode

In this mode, the CPU is halted, with the peripheral hardware operated by the low-frequency clock (fs). The same procedure is followed to activate the SLEEP mode and return to the SLOW mode as in the IDLE mode. (Refer to the operation mode transition diagram in Figure 3.3.4 (a).)

### STOP mode

All system operations including oscillating circuit stop under this mode. The device keeps the internal condition under low current consumption. In this case, the I/O port output state can be selected for all ports collectively between output retention or high-impedance state by the watchdog timer control register 1 WDTCR1 <DRVE>. In order to set device to STOP mode, set watchdog timer control register 2 WDTCR2 <HALT1, 0> to STOP mode and execute HALT instruction. Releasing is done by external interrupt INTO (P50) or INT1 (P51) (Interrupt generation timing is selected either rising edge or falling edge). After the period for warming-up, the device restarts from the instruction followed by HALT instruction when interrupt is disabled. And it restarts after interrupt routine when interrupt is enabled.

(a) Operation Mode Transition Diagram

| Operation | Ocsil           | lator         | CPU   | Desistant  | System             |  |

|-----------|-----------------|---------------|-------|------------|--------------------|--|

| Mode      | High freq. (fc) | Lowfreq. (fs) |       | Peripheral | Clock              |  |

| RESET     |                 | Stop          | Reset | Reset      |                    |  |

| NORMAL    | Osc.            | Osc.<br>or    | Run   | Operation  | High-<br>frequency |  |

| IDLE      |                 | Stop          | Stop  | (Note 1)   |                    |  |

| SLOW      |                 |               | Run   | (Note 2)   | Low-               |  |

| SLEEP     | Stop            | Osc.          |       | (Note 1)   | frequency          |  |

| STOP      |                 | Stop          | Stop  | Stop       | Stop               |  |

(b) Device status in each operation mode

- Note 1) The I/O ports retain the previous status immediately before the HALT instruction is executed. The peripheral circuits only (1) time-base counter (TBC), (2) watchdog timer (WDT), (3) realtime counter (RTC), and (4) interrupt control circuit are operating.

- Note 2) The operating circuits in this case are (1) I/O ports, (2) time-base counter (TBC), (3) watchdog timer (WDT), (4) real-time counter (RTC), and (5) interrupt control circuit. (All other peripheral circuits and their interrupts must be disabled before they are placed in the SLOW mode.)

Figure 3.3.4 Operation mode transition diagram and device status

9097249 0043670 647 🔳

MCU90-403

### System Control Resister 1

SYSCR1 (FFBOH)

| 7      | 6     | 5                     | 4    | 3         | 2         | 1        | 0                                                          |                                                                                    |  |  |  |  |

|--------|-------|-----------------------|------|-----------|-----------|----------|------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|--|

|        | SYSCK | XEN                   | XTEN | RXEN      | RXTEN     | RSYSCK   | WUEF                                                       | (Reset Value +010 1000)                                                            |  |  |  |  |

| SYSCK  |       | (W)Syste<br>(R) Mon   |      | Mode      | Select    |          | 0 : High Frequency Clock Mode 1 : Low Frequency Clock Mode |                                                                                    |  |  |  |  |

| XEN    |       | (W)High<br>(R) Mon    | •    | ncy Osci  | llator Co | ontrol   | 0 : Stop Oscillation<br>1 : Continue / Restart Oscillation |                                                                                    |  |  |  |  |

| XTEN   |       | (W)Low<br>(R) Mon     |      | ncy Oscil | llator Co | ontrol   | 0 : Stop Oscillation 1 : Continue / Restart Oscillation    |                                                                                    |  |  |  |  |

| RXEN   |       | High Fre<br>after res | • •  |           |           |          | 0                                                          | : Stop Oscillation<br>: Restart Oscillation R/W                                    |  |  |  |  |

| RXTEN  |       | Low Free<br>restartin | • •  |           |           | ol after | 0                                                          |                                                                                    |  |  |  |  |

| RSYSCI | ĸ     | System (<br>restartin |      |           |           |          | 0                                                          | High Frequency Clock Mode     Low Frequency Clock Mode                             |  |  |  |  |

| WUEF   |       | (W)War<br>(R) War     |      |           |           | bl       | 0                                                          | : (W) –<br>(R) Warming-up Complete<br>: (W) Warming-up Start,<br>(R) In Warming-up |  |  |  |  |

### System Control Resister 2

SYSCR2 (FFB1H)

| 2 7    | 6                                      | 5      | 4       | 3        | 2      | 1      | 0                                  |                                                      |  |  |  |

|--------|----------------------------------------|--------|---------|----------|--------|--------|------------------------------------|------------------------------------------------------|--|--|--|

| )      |                                        |        | RTCCK   | RTCST    | RTCIS1 | RTCIS0 | WARM                               | (Reset Value ***0 0000)                              |  |  |  |

| DICCK  | RTCCK RTC Clock Source Select          |        |         |          |        |        | 0                                  | : Low Frequency Clock                                |  |  |  |

| RICCK  |                                        | RICCIO | K SOULC | e Select |        |        | 1                                  | : High Frequency Clock                               |  |  |  |

| DICCT  | RTCST RTC Start Control                |        |         |          |        |        | 0                                  | : Stop and Counter Clear                             |  |  |  |

| RICSI  |                                        |        |         |          |        |        | 1                                  | : Start                                              |  |  |  |

|        |                                        |        |         |          |        |        | 00                                 | : fc/2 <sup>15</sup> or fs/2 <sup>15</sup> (1.0) [s] |  |  |  |

| RTCIS1 |                                        |        |         |          | DTC    |        | 01                                 | : fc/2 <sup>16</sup> or fs/2 <sup>16</sup> (2.0) [s] |  |  |  |

|        | Interval Time Control of RTC Interrupt |        |         |          |        | errupt | 01 10 : fc/214 or fs/214 (0.5) [s] |                                                      |  |  |  |

| RTCISO |                                        |        |         |          |        |        |                                    | : Inhibited                                          |  |  |  |

|        |                                        |        |         |          |        |        |                                    | : 214/fc or 214/fs [s]                               |  |  |  |

| WARM   | VARM Warming-up Time Select            |        |         |          |        |        | 1                                  | : 216/fc or 216/fs [s]                               |  |  |  |

### Watchdog Timer Control Register 1

| WDTCR1  | 7    | 6 | 5                     | 4     | 3    | 2 1       | 1   | 0    |                                                                                                   |     |    |

|---------|------|---|-----------------------|-------|------|-----------|-----|------|---------------------------------------------------------------------------------------------------|-----|----|

| (FFFBH) |      |   | TBC1F                 | TBCOF | WDTE |           | EXF | DRVE | (Reset Value **00 0*00)                                                                           |     |    |

|         | DRVE |   | Controlli<br>during S |       |      | is for po | rt  | 0    | <ul> <li>High Impedance</li> <li>Keep the status throughout setting STOP</li> <li>mode</li> </ul> | R/W | ]. |

Watchdog Timer Control Register 2

| WDTCR1  | 7     | 6 | 5       | 4          | 3      | 2     | 1      | 0            |                                      |     |

|---------|-------|---|---------|------------|--------|-------|--------|--------------|--------------------------------------|-----|

| (F797H) |       |   |         |            | WDTP1  | WDTPO | HALTM1 | HALTM0       | (Reset Value **** 0000)              |     |

|         | HALTM | 1 | Cottin  | g Stand-by | , mode |       |        | 00 :<br>01 : | -<br>STOP mode                       | R/W |

|         | HALTM | ) | setting | y stand-by | , mode |       |        | 10 :<br>11 : | IDLE mode or SLEEP mode<br>don't use |     |

### MCU90-404

🛛 9097249 0043671 583 🖿

# 3.3.4 Controlling Operation Mode

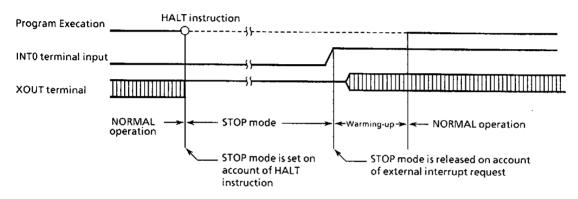

### (1) STOP mode

STOP mode is to be set by executing HALT instruction when watchdog timer control register 2 WDTCR2 <HALT1, 0> = "01". During STOP mode, both high frequency and low frequency stop oscillation and all operations are stopped. Data memory, registers, output laches for ports keep the status of just before the HALT instruction. The output for ports is selected whether to keep output or to be high impedance by setting <DRVE> in watchdog timer control register 1 (WDTCR1).

Releasing STOP mode is done by interrupt or resetting. If CPU is EI (interrupt master enable flag IFF is "1"), the interrupt is accepted and CPU starts interrupt processing. If CPU is DI (interrupt enable flag IFF is "0"), CPU restart from the instruction followed by HALT; in this case, the interrupt request flag for releasing is required to be cleared after releasing.

If STOP mode is released by resetting (RESET terminal to "L" level), even though the register setting for returned mode is SLOW mode, the device restarts from NORMAL mode.

Figure 3.3.5 Sequence example for STOP mode

STOP mode is released by following sequence.

① The oscillation starts. By setting system control register 1 SYSCR1 <RXEN, RXTEN, RSYSCK>, the operation mode after the STOP mode can be selected; setting the register <RXEN, RXTEN, RSYSCK> should precede HALT instruction for STOP mode.

|                           | <rxen></rxen> | <rxten></rxten> | <rsysck></rsysck> |

|---------------------------|---------------|-----------------|-------------------|

| Recovering to NORMAL mode | 1             | 0               | 0                 |

| Recovering to SLOW mode   | 0             | 1               | 1                 |

Table 3.3.2 Operation Mode Setting after Exiting STOP Mode

- Note 1) If an interrupt request for releasing STOP mode occur when the "HALT" instruction is executed, the operation mode which is determined by SYSCR1<SYSCK, XEN, XTEN> at the execution of HALT instruction will be maintained.

- Note2) The operation mode can be confirmed by reading system control register SYSCR1 < SYSCK, XEN, XTEN>.

- Warming-up is executed in order to keep time waiting for stabilizing oscillation. During warming-up, the internal operation is still stopping. Time length for warming-up can be selected from 2 on system control register 2 SYSCR2 <WARM> to fit an oscillation characteristics.

The clock source for warming-up counter is selected by hardware; high frequency clock (fc) is to recover NORMAL mode and low frequency clock (fs) is to recover SLOW mode.

| <warm></warm> | To operate in<br>NORMAL mode<br>(@ fc = 16 [MHz]) | To operate in<br>SLOW mode<br>(@ fs = 32.768 [kHz]) |

|---------------|---------------------------------------------------|-----------------------------------------------------|

| 0             | 1.024 ms                                          | 500 ms                                              |

| 1             | 4.096 ms                                          | 2 s                                                 |

Table 3.3.3 Warming-up Time (When Exiting STOP Mode)

③ After warming-up time is completed, normal operation (NORMAL mode or SLOW mode) is restarted.

#### (2) IDLE (SLEEP) mode

The IDLE (SLEEP) mode is entered by executing a HALT instruction after setting the watchdog timer control register 2 (WDTCR2) <HALTM1, HALTM0> to '10'. In this mode, the CPU stops operating, with part of the peripheral circuits continuing operation. (Refer to the device status in each operation mode in Figure 3.3.4 (b).)

The IDLE (SLEEP) mode is released by an interrupt request or a reset (with the RESET pin pulled low). If a non-maskable interrupt or a maskable interrupt is in El state, an interrupt routine will be executed after releasing from the IDLE (SLEEP) mode. If the interrupt is in DI state, an instruction next to the HALT will be executed after releasing from the IDLE (SLEEP) mode. The interrupt requeset flag which is used as a mode releasing signal should be cleared to "0".

The interrupt source that can be used to release the IDLE (SLEEP) mode is (1) watchdog timer interrupt (INTWDT), (2) timebase counter interrupt (INTTBC), (3) realtime counter interrupt (INTRTC), (4) external interrupt (INT0), or (5) external interrupt (INT1).

If the device is reset when in IDLE (SLEEP) mode, the device starts up from the NORMAL mode.

### (3) SLOW mode

The SLOW mode is controlled by system control register 1, 2 (SYSCR1, 2) and warming-up counter.

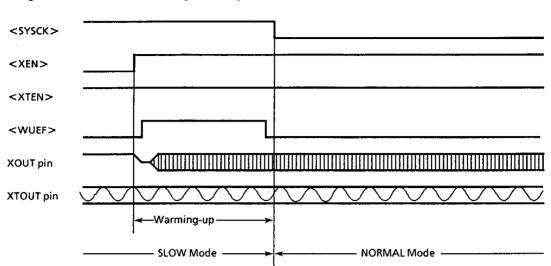

#### ① Switch over from NORMAL to SLOW mode

First, set the SYSCR1 <XTEN> to "1" to activate the low-frequency clock (fs). After the oscillation stabilizes, set the SYSCR1 <SYSCK> to "1" to switch over the system clock to the low-frequency clock (fs) (The low-frequency clock (fs) had better been already oscillating at the beginning of application program). Then reset the SYSCR1 <XEN> to "0" to stop the high-frequency oscillator.

It may be convenient to use the warming-up counter to confirm the stabilized low-frequency clock (fs). The warming-up counter starts counting the low-frequency clock (fs) by setting the SYSCR1 <WUEF> to "1". The <WUEF> bit is cleared to "0" after an elapse of the warming-up time that is set in the SYSCR2 <WARM>.

Table 3.3.4 shows the warming-up time at which the mode is switched over from NORMAL to SLOW.

| <warm></warm> | @ fs = 32.768 [kHz] |  |  |  |  |

|---------------|---------------------|--|--|--|--|

| 0             | 500 ms              |  |  |  |  |

| 1             | 2 s                 |  |  |  |  |

Table 3.3.4 Warming-up time (for shifting from NORMAL to SLOW mode)

Note 1) The warming-up time is derived by dividing the low-frequency clock (fs) by the warming-up counter. For this reason, the warming-up time includes an error, because of the unstable oscillation at the start-up. Therefore, the warming-up time must be handled as an approximate value.

Note 2) If the low-frequency clock (fs) does not have its oscillation stabilized even when the warming-up flag <WUEF> is cleared to "0", perform warming-up operation several times until the oscillation stabilizes.

Figure 3.3.6 shows a switching over sequence from NOMAL to SLOW mode.

Figure 3.3.6 Switching over sequence from NORMAL to SLOW mode

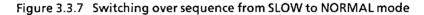

② Switch over from SLOW to NORMAL mode

First, set the SYSCR1 <XEN> to "1" to acrivate the high-frequency clock (fc) to start oscillating. After waiting for the oscillation to stabilize, reset the SYSCR1 <SYSCK> to "0" to switch the system clock from the low-frequency to the high-frequency clock (fc).

It may be convenient to use the warming-up counter to confirm the stabilized high-frequency clock (fc). The warming-up counter starts counting the high-frequency clock (fc) by setting the SYSCR1 <WUEF> to "1". The <WUEF> is cleared to "0" after an elapse of the warming-up time that is set in the SYSCR2 <WARM>.

Table 3.3.5 shows the warming-up time at which the mode is switched over from SLOW to NORMAL.

Table 3.3.5 Warming-up time (for shifting from SLOW to NORMAL mode)

| <warm></warm> | @ fc = 16 [MHz] |

|---------------|-----------------|

| 0             | 1.024 ms        |

| 1             | 4.096 ms        |

- Note 1) The warming-up time is derived by dividing the high-frequency clock (fc) by the warming-up counter. For this reason, the warming-up time includes an error, because of the unstable oscillation at the start-up. Therefore, the warming-up time must be handled as an approximate value.

- Note 2) If the high-frequency clock (fc) does not have its oscillation stabilized even when the warmingup flag <WUEF> is cleared to "0", perform warming-up operation several times until the oscillation stabilizes.

MCU90-407 9097249 0043674 292

Figure 3.3.7 shows a switching over sequence from SLOW to NORMAL mode.

### **3.3.5** Real Time Counter (RTC)

The TMP90CR74A has the real time counter (RTC) which generates a periodic interrupt request. The RTC is controlled by System Control Register2 (SYSCR2).

The RTC is a 17bit binary counter and its clock source is selected either low frequency clock (fs) or high frequency clock (fc/4). To start/stop the counter is controlled by <RTCST>.

The period of interrupt request INTRTC is selected from 3 types by setting <RTCIS1, RTCIS0>. Table 3.3.6 shows the period of interrupt request INTRTC.

| <rtcck></rtcck>   | <rtcis 0="" 1,=""></rtcis> | INTRTC interrupt<br>interval |

|-------------------|----------------------------|------------------------------|

| 0                 | 00                         | 1 s                          |

| (fs = 32.768 kHz) | 01                         | 2 s                          |

|                   | 10                         | 0.5 s                        |

| 1                 | 00                         | 8.192 ms                     |

| (fc = 16 MHz)     | 01                         | 16.384 ms                    |

|                   | 10                         | 4.196 ms                     |

Table 3.3.6 INTRTC Interrupt Interval

MCU90-408

9097249 0043675 129 🖿

# 3.4 INTERRUPT CONTROLLER

The TMP90CR74A has 18 types (external : 2, internal : 16) of interrupt factors (As a source, 2 types for external and 18 types for internal; totaled 20). Two of internal are non-maskable and others are maskable.

The interrupt factor has own interrupt request flag (IRF) to keep the request for interrupt; every interrupt request flag has a vector independently. Interrupt request flag is set to "1" on occurring of interrupt request and requires acceptance for interrupt to CPU.

The acceptance for each interrupt can be enable independently by interrupt enable flag (IFF) and Interrupt Enable register (INTE). If the plural interrupt are generated simultaneously, the interrupt with higher priority is accepted first; the priority is fixed on hardware.

| Priorit | ty                      | Interrupt Sources                  | Туре         | Clear Code for<br>Interrupt | Vector address |

|---------|-------------------------|------------------------------------|--------------|-----------------------------|----------------|

| Highest | 1                       | INTSWI (Software Interrupt)        |              |                             | 0008H          |

|         | 2                       | INTWDT (Watchdog Timer)            | Non Maskable | _                           | 000CH          |

|         | 3                       | INTO (External input 0)            |              | 04H                         | 0010H          |

|         | 4                       | INTCAP1 (Capture 1)                |              | 05H                         | 0014H          |

|         | 5                       | INTCAP0 (Capture 0)                |              | 06Н                         | 0018H          |

|         | 6                       | INTTPG0 (Timing Pulse Generator 0) |              | 07H                         | 001CH          |

|         | 7                       | INTTPG1 (Timing Pulse Generator 1) |              | 08H                         | 0020H          |

|         | 8                       | INTIIC (I <sup>2</sup> CBus)       |              | 09н                         | 0024H          |

|         | 9                       | INTTBC (Time Base Counter)         |              | 0AH                         | 0028H          |

| 10      | INTTO (Timer Counter 0) |                                    |              |                             |                |

|         | 10                      | INTDIR (Capstan invert detection)  |              | ОВН                         | 002CH          |

|         | 11                      | INTSIO0 (Serial Interface 0)       | Maskable     | ОСН                         | 0030H          |

|         | 12                      | INTSIO1 (Serial Interface 1)       |              | 0DH                         | 0034H          |

|         | 13                      | INTT1 (Timer Counter 1)            |              | OEH                         | 0038H          |

|         | 14                      | INTT2 (Timer Counter 2)            |              | 0FH                         | 003CH          |

|         | 45                      | INTT3 (Timer Counter 3)            |              |                             |                |

| 1       | 15                      | INTAD (A/D conversion)             |              | 10H                         | 0040H          |

|         | 16                      | INTVA (VISS/VASS detection)        |              | 11H                         | 0044H          |

|         | 17                      | INT1 (External input 1)            |              | 12H                         | 0048H          |

| Lowest  | 18                      | INTRTC (Real Time Counter)         |              | 13H                         | 004CH          |

| Table 3.4.1 | Interru | pt Sources |

|-------------|---------|------------|

|-------------|---------|------------|

MCU90-409

I 90972490043676065 🎟

When an interrupt is requested by software or from internal I/O block the interrupt request is transferred to the CPU via an interrupt controller. The CPU starts the interrupt processing if it is a non-maskable or maskable interrupt requested in the EI state (Interrupt enable flag (IFF) = "1"). However, a maskable interrupt requested in the DI state (IFF = "0") is ignored.

Having acknowledged an interrupt, the CPU reads out the interrupt vector from the interrupt controller and jumps to an interrupt routine.

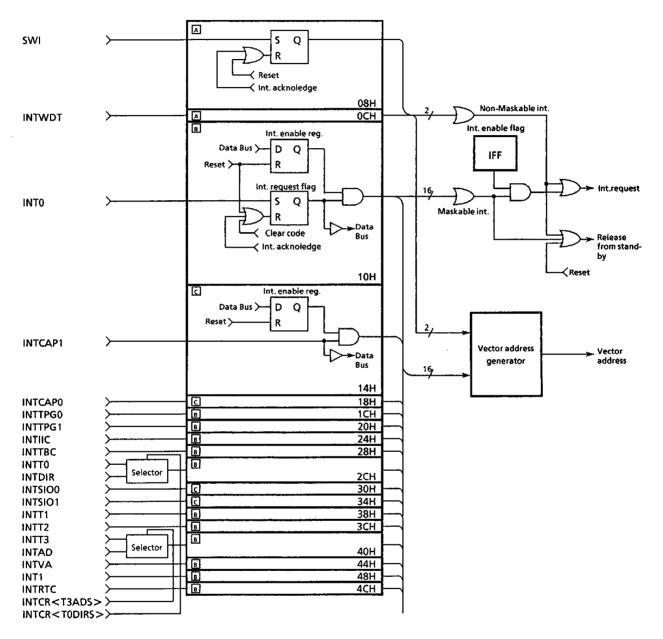

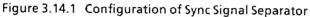

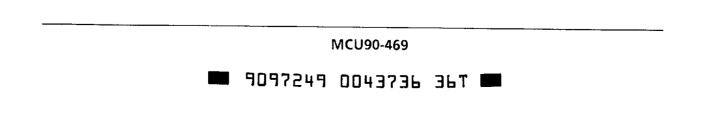

Figure 3.4.1 Configuration of Interrupt Controller

MCU90-410

| 9097249 0043677 TTL 🔳

### 3.4.1 Interrupt processing

A non-maskable interrupt can't be disabled by programming. A maskable interrupt, on the other hand, can be enabled or disabled by programming.

An interrupt enable flag (IFF) is assigned on the bit 5 of Register F in the CPU. The interrupt is enabled or disabled by setting IFF to "1" by the El instruction or to "0" by the Dl instruction, respectively. IFF is reset to "0" by the Reset operation or the acceptance of interrupt. The interrupt can be enabled after the subsequent instruction of El instruction is executed.

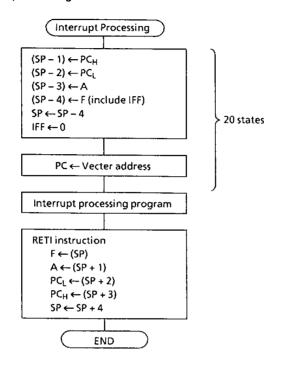

Fig. 3.4.2 shows an interrupt processing flowchart.

Figure 3.4.2 Interrupt Processing Flowchart

The CPU stores the contents of program counter (PC) and the register pair AF (including the interrupt enable flag (IFF) before the accepting interrupt) into the stack, and resets the interrupt enable flag (IFF) to "0" (disable interrupts). Then, an interrupt controller transfers the interrupt vector to the program counter, and the program jumps to the interrupt routine. When vector has been read out, interrupt request flag (IRF) is cleared to "0".

The overhead from accepting an interrupt to jumping to an interrupt routine is 20 states (2.5 Is at fc = 16 MHz).

An interrupt (Maskable and Non-maskable) routine is completed by a RETI instruction. When the RETI instruction is executed, the data previously stacked from the program counter (PC) and the register pair (AF) are restored. Then, the interrupt enable flag (IFF) returns to the state before the interrupt.

### 3.4.2 Interrupt Controller

The "priority" in the Table3.4.1 means the order of the interrupt source to be acknowledged by the CPU when plural interrupts are requested at the same time. If interrupts of 3rd and 4th priorities are requested simultaneously, for example, CPU accepts an interrupt of 3rd priority, first. After the 3rd priority interrupt processing has been completed by a RETI instruction, the CPU accepts an interrupt of 4th priority. If an El instruction is executing in the 3rd priority interrupt routine, then the 4th priority interrupt is accepted.

The interrupt controller merely determines the priority of the sources of interrupts to be accepted by the CPU when plural interrupts are requested at the same time. It is, therefore, unable to compare the priority of interrupt being executed with the one being requested. In order to permit another interrupt during a certain interrupt routine, set the interrupt enable register (INTE1/INTE2) for the interrupt to be allowed and execute the El instruction.

Fig.3.4.1 shows a configuration of the interrupt controller. The interrupt controller consists of Interrupt Request Flag (IRF) and Interrupt Enable register (INTE) allocated to each of interrupt channels. The interrupt request flag (IRF) is a flip-flop to maintain an interrupt request from internal I/O. Each flip-flop is reset to "0" by resetting or reading out the vector by CPU when an interrupt is accepted. The interrupt request flag (IRF) can be reset by an instruction which write clear code (Refer to Table 3.4.1) to the address F790 (H).

Example) In case of resetting the interrupt request flag of INTO (External interrupt 0), write the clear code "04 (H)" to the address F790 (H).

LD (F790H), 04H

The state of interrupt request flag (IRF) can be checked by reading the address F790(H) for IRF1 and F791(H) for IRF2.

#### Caution) The clear code must be written in DI state.

Note) Following 4 interrupt sources in 16 maskable interrupts don't have interrupt request flag. Refer to the explanation of individual I/O function about clearing the interrupt request.

INTCAP0 :Interrupt from Capture 0INTCAP1 :Interrupt from Capture 1INTSIO0 :Interrupt from SIO 0INTSIO1 :Interrupt from SIO 1

The Interrupt Enable registers (INTE) are assigned to the address F78D (H):INTE1 and F78E (H):INTE2. Setting any of these bits to "1" enables an interrupt of the respective channel and "0" disables an interrupt. These bits are initialized to "0" by resetting.

### MCU90-412

# 9097249 0043679 874 🎟

### 3.4.3 Interrupt Control Register

Followings are bit function of Interrupt Request Flag (IRF1, IRF2), Interrupt Enable Register (INTE1, INTE2) and Interrupt Control Register (INTCR).

| Interrupt | Request | Flag 1 |

|-----------|---------|--------|

|-----------|---------|--------|

| Request Flag 1<br>7 6 | 5 4 3 2 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                       |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

|                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                       |

| ·                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                       |

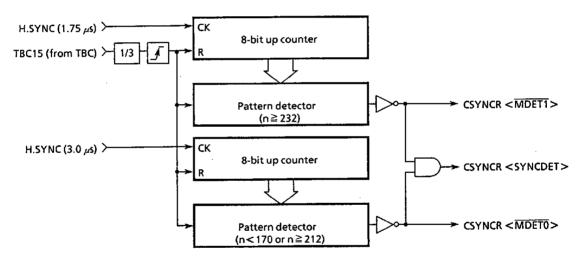

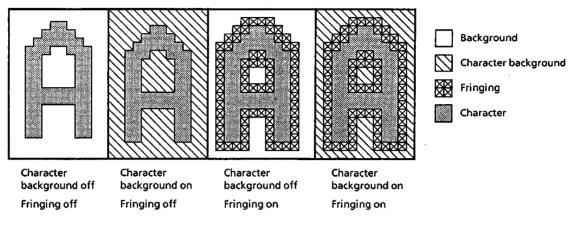

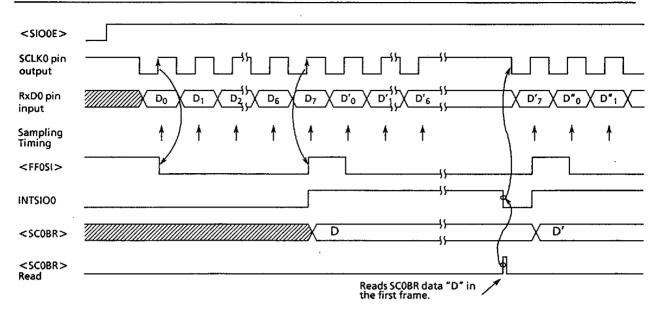

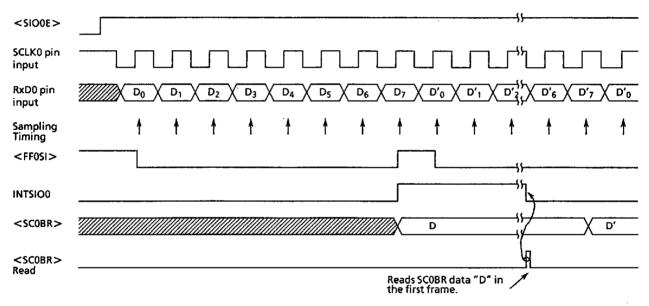

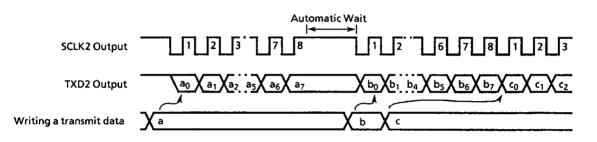

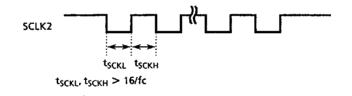

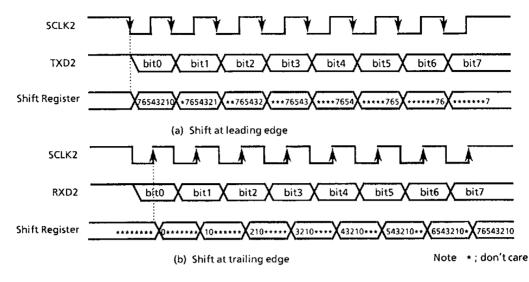

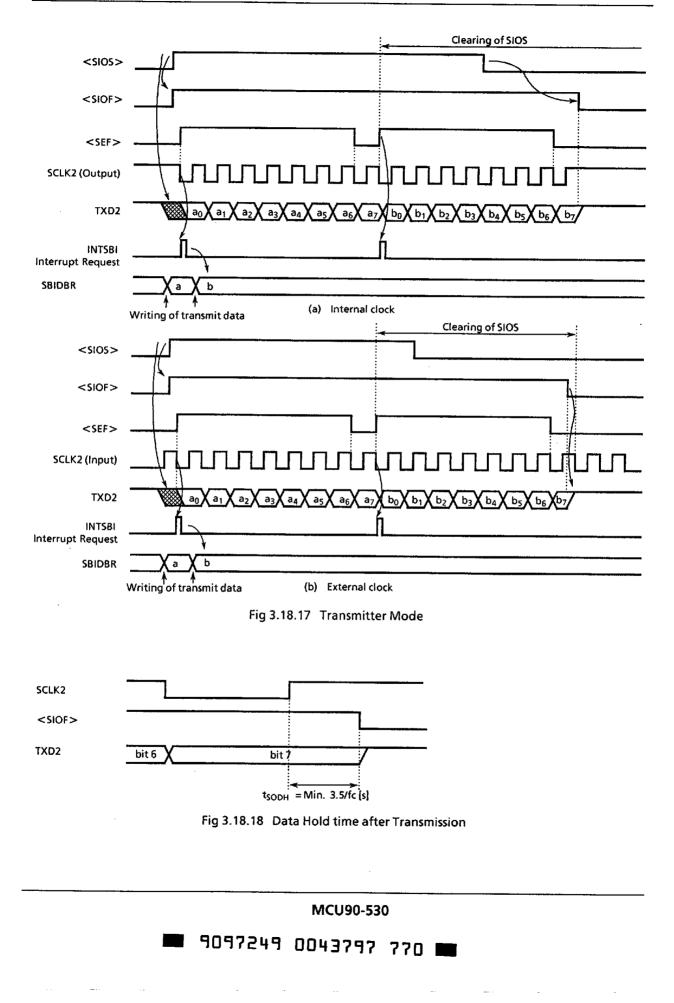

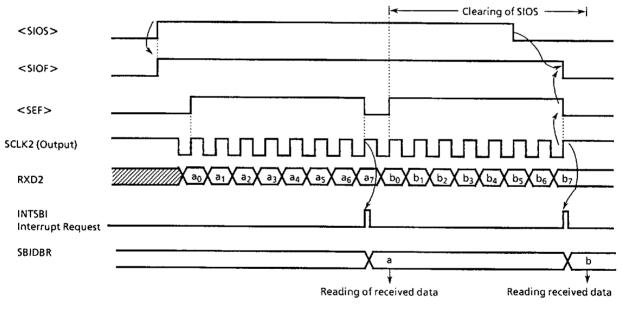

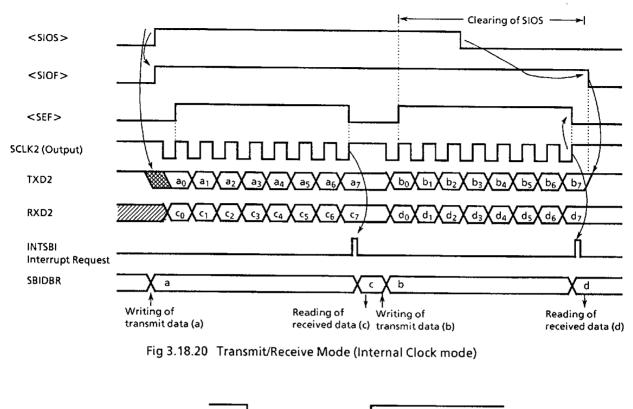

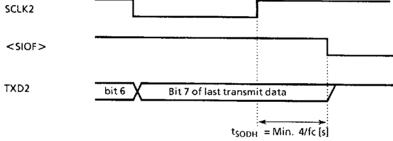

|                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                       |